CMOS: NOT Gate Design Process

By:

Anurag

Verma (17)

Garima

Verma (31)

PGDIE

42

1.

Introduction:

Complementary-metal-oxide-semiconductor (CMOS)

is a technology

used for constructing integrated

circuits

(ICs). CMOS technology is used in microprocessors, microcontrollers, static

RAM,

and other digital

logic circuits. CMOS is also

sometimes referred to as complementary-symmetry

metal–oxide–semiconductor (COS-MOS).The words

"complementary-symmetry" refer to the fact that the typical digital

design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field

effect transistors (MOSFETs) for logic

functions like NOT,NAND,NOR etc. CMOS devices do not produce as much waste heat as other forms of

logic. CMOS also allows a high density of logic functions on a chip. It was

primarily for this reason that CMOS became the most used technology to be

implemented in VLSI chips. The phrase

"metal–oxide–semiconductor" is a reference to the physical structure

of certain field-effect

transistors,

having a metal gate electrode placed on top of an oxide insulator, which in

turn is on top of a semiconductor

material.

NOT gate is

implemented in CMOS by a combination of p-MOS and n-MOS as shown in Figure 1.2.

It is designed based on λ-based rules and stick diagram. The fabrication

process has been

discussed below for

CMOS inverter.

2.

Symbols

and Terminologies used in CMOS:

2.1.

Terminologies used for

CMOS

Symbol

|

Parameter

|

Value

|

Unit

|

Vcc

|

Supply Voltage

|

0 to 5

|

Volts

|

Vi

|

Input Voltage

|

0/5

|

Volts

|

Vo

|

Output Voltage

|

5/0

|

Volts

|

2.2.

Symbol of NOT Gate

Fig 1.1: Symbol for NOT Gate

2.3.

Truth

Table for NOT GATE

Input : A

|

Output: X

|

1

|

0

|

0

|

1

|

2.4.

CMOS

repesentation of NOT GATE

Fig 1.2: nMOS and

pMOS combined to form a NOT Gate

3.Design

Process

Sr.No.

|

Process

|

Diagram

|

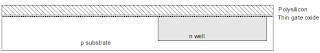

1.

|

Ø Start with blank

wafer

Ø Build inverter from

the bottom up

Ø First step will be

to form the n-well

·

Cover

wafer with protective layer of SiO2 (oxide)

·

Remove

layer where n-well should be built

·

Implant

or diffuse n dopants into exposed wafer

·

Strip

off SiO2

|

|

2.

|

Ø Grow SiO2

on top of Si wafer

· 900 – 1200 C with H2O

or O2 in oxidation furnace

|

|

3.

|

Ø Spin on photoresist

· Photoresist is a

light-sensitive organic polymer

·

Softens

where exposed to light

|

|

4.

|

Ø Expose photoresist

through n-well mask

Ø Strip off exposed

photoresist

|

|

5.

|

Ø Etch oxide with

hydrofluoric acid (HF)

Ø Only attacks oxide

where resist has been exposed

|

|

6.

|

Ø Strip off remaining

photoresist using mixture of acids called piranah etch to

avoid resist

melting

|

|

7.

|

Ø n-well is formed

with diffusion or ion implantation

Ø Diffusion

·

Place

wafer in furnace with arsenic gas

·

Heat

until As atoms diffuse into exposed Si

Ø Ion Implantation

·

Blast

wafer with beam of As ions

·

Ions

blocked by SiO2, only enter exposed Si

|

|

8.

|

Ø Strip off the

remaining oxide using HF

Ø Back to bare wafer

with n-well

Ø Subsequent steps

involve similar series of steps

|

|

9.

|

Ø Deposit very thin

layer of gate oxide

·

<

20 Å (6-7 atomic layers)

Ø Chemical Vapor

Deposition (CVD) of silicon layer

·

Place

wafer in furnace with Silane gas (SiH4)

· Forms many small

crystals called polysilicon

· Heavily doped to be

good conductor

|

|

10.

|

Ø Use same lithography

process to pattern polysilicon

|

|

11.

|

Ø Use oxide and

masking to expose where n+ dopants should be diffused or implanted

Ø N-diffusion forms

nMOS source, drain, and n-well contact

|

|

12.

|

Ø Pattern oxide and

form n+ regions

Ø Self-aligned process where gate blocks

diffusion

Ø Polysilicon is

better than metal for self-aligned gates because it doesn’t melt during later

processing

|

|

13.

|

Ø Historically dopants

were diffused

Ø Usually ion

implantation today

Ø But regions are

still called diffusion

|

|

14.

|

Ø Strip off oxide to

complete patterning step

|

|

15.

|

Ø Similar set of steps

form p+ diffusion regions for pMOS source and drain and substrate contact

|

|

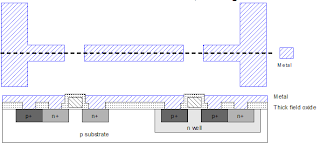

16.

|

Ø Now we need to wire together

the devices

Ø Cover chip with

thick field oxide

Ø Etch oxide where

contact cuts are needed

|

|

17.

|

Ø Sputter on aluminum

over whole wafer

Ø Pattern to remove

excess metal, leaving wires

|

4.

λ-based Design Rules for CMOS Fabrication

Rule

number Description λ-Rule

Active area rules

R1 Minimum active

area width

3λ

R2 Minimum active

area spacing

3λ

Polysilicon rules

R3 Minimum poly

width

2λ

R4 Minimum poly

spacing 2λ

R5 Minimum gate

extension of poly over active

2λ

R6 Minimum

poly-active edge spacing

1λ

(poly

outside active area)

R7 Minimum

poly-active edge spacing

3λ

(poly

inside active area)

Metal rules

R8 Minimum metal

width 3λ

R9 Minimum metal

spacing 3λ

Contact rules

R10 Poly contact size

2λ

R11 Minimum poly

contact spacing 2λ

R12 Minimum poly

contact to poly edge spacing

1λ

R13 Minimum poly

contact to metal edge spacing 1λ

R14 Minimum poly

contact to active edge spacing 3λ

R15 Active contact

size

2λ

R16 Minimum active

contact spacing 2λ

(on

the same active region)

R17 Minimum active

contact to active edge spacing 1λ

R18 Minimum active

contact to metal edge spacing 1λ

R19 Minimum active

contact to poly edge spacing 3λ

R20 Minimum active

contact spacing 6λ

(on

different active regions)

5.

STICK Diagram:

Fig 1.4: λ based layout diagram for NOT Gate

6.

Equipments used in Manufacturing:

Sr.No.

|

Process

|

Equipment Used

|

1.

|

Evaporation

(Deposition)

|

Vacuum

Pump

|

2.

|

Photolithography

|

Stepper

and Photo Mask

|

3.

|

Etching

|

Reactive

Ion Etching (RIE) System

|

4.

|

Diffusion

|

Heating

in Quartz Tube at 900-1100 degree C

|

5.

|

Ion

Implantation

|

Ion

Beams of purified Dopants

|

Fig 1.5:Testing procedure for CMOS

5.1

Designing the logic

The

objective of the design procedure is to produce a CMOS NOT Gate. In this

specification what operation the gate has to perform is done. Inputs and

outputs the Gates are decided.

5.2

Synthesizing the gates

The

objective of the synthesis procedure is to generate a gate-level net-list

equivalent to the logic created in the design procedure.

5.3

Laying out the chip

The

objective of the layout procedure is to generate the actual geometries that

form the masks to build the chip. The layout process defines the actual

patterns that are created on the chip. The vendor uses powerful CAD tools to

determine how to actually arrange the CMOS wafer then simulator is used to verify

that the design’s function and timing are correct before fabricating the chip.

5.4

Fabricating the prototypes

The

objective of the fabrication process is to manufacture prototype ICs. Vendors

produce prototypes before mass production for speed and quality control. They

run two or three wafers of the chip so that if something goes wrong on one

wafer, the other wafers may still yield good parts. Turnaround time for

prototypes is four to eight weeks. Once the prototype chips have been

fabricated and delivered, the next task is to verify their functionality and

working.

5.5

Verifying the prototypes

The

objective of the verification process is to ensure that the prototype ICs meet

all their functional, timing, environmental requirements and also meet the

needs of the system they were designed to be part of. The prototype chips need

to be evaluated quickly because the process will be delayed if the ASIC has

problems. If verification testing proves that the chip meets all of its

specifications and functionality, then the process of developing the ASIC is

completed. The design is released for production. However, problems often arise

during verification. Sometimes they can be tolerated or can be worked around in

software; if not iteration of the design has to be performed.

5.6

Iterating the design

The

objective of iteration process is to revise the design until the prototype

chips pass the verification process. CAD tools and vendors are so good these

days, first set of prototypes often yields good parts. However, when bugs do

show up, they are eliminated by revising the design and prototyping the chip

again. This process is known as iterating the chip, or stepping the chip. What

it means is that we return to the beginning of the design procedure and do it

all over again. Subsequent iterations can be accomplished much more quickly

than the first pass because we can focus on just the few problems that require

fixing. Finally when the prototype passes the verification process, CMOS NOT

Gate development process is completed.